반도체 패키징

본 서비스가 제공하는 내용 및 자료가 사실임을 보증하지 않습니다. 시스템은 언제나 실수를 할 수 있습니다. 중요한 의사결정 및 법리적 해석, 금전적 의사결정에 사용하지 마십시오.

반도체 패키징은 전공정을 거쳐 완성된 웨이퍼의 칩을 개별적으로 분리하여 외부와 전기 신호를 주고받을 수 있도록 연결하고, 습도나 충격 등 외부 환경으로부터 보호하는 반도체 제조의 마지막 단계이다. 과거에는 단순한 포장 기술로 인식되었으나, 최근 미세공정의 물리적 한계를 극복하기 위한 첨단 패키징 기술이 반도체 성능 향상의 핵심 요소로 부상하고 있다.

개요 및 역할

반도체 패키징은 반도체 8대 공정 중 마지막 단계에 해당한다. 전공정을 마친 웨이퍼 상태의 칩은 외부와 전기 신호를 주고받을 수 없으며 충격에 취약하다. 패키징은 이러한 칩을 전자기기에 장착 가능한 형태로 만들고, 고온, 고습, 진동 등 외부 환경으로부터 회로를 보호하는 역할을 한다. 또한 칩에서 발생하는 열을 효과적으로 배출하여 안정적인 동작을 돕는다.

주요 구성 요소

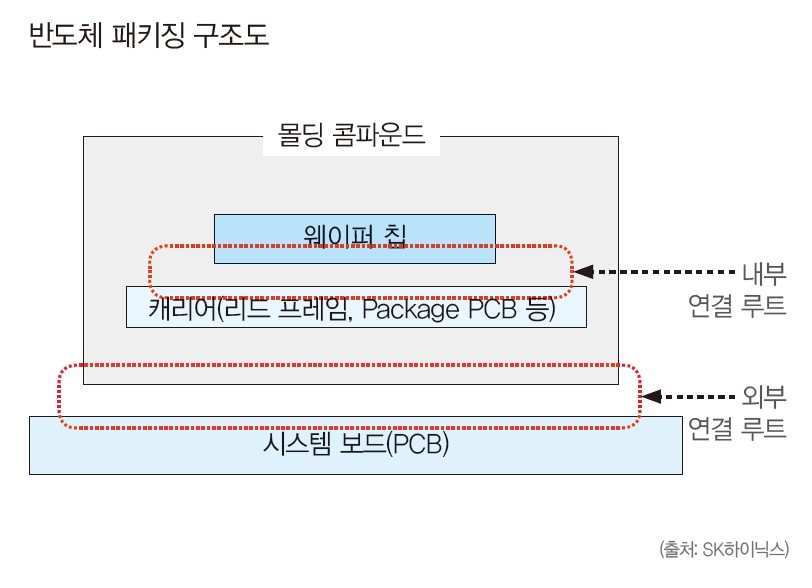

반도체 패키지는 다음과 같은 요소들로 구성된다.

- 실리콘 칩(Die): 웨이퍼에서 잘라낸 실제 반도체 소자이다.

- 기판(Substrate): 칩을 실장하는 용기로, 칩과 메인 인쇄회로기판(PCB) 사이의 전기적 통로 역할을 한다.

- 연결 소재: 칩과 기판을 연결하는 금속선(와이어)이나 돌기 형태의 범프(Bump)가 사용된다.

- 몰딩 컴파운드(EMC): 칩을 외부 충격으로부터 보호하기 위해 감싸는 밀봉재이다.

- 솔더볼(Solder Ball): 패키지 하단에 부착되어 메인 보드와 연결되는 전도성 구체이다.

공정 순서

패키징 공정은 일반적으로 다음과 같은 순서로 진행된다.

- 웨이퍼 절단(Dicing): 웨이퍼에 배열된 수백 개의 칩을 스크라이브 라인을 따라 낱개로 분리한다. 분리된 칩은 베어칩(Bare chip) 또는 다이(Die)라고 부른다.

- 칩 부착(Die Attach): 분리된 칩을 기판이나 리드프레임 위에 고정한다.

- 연결(Bonding): 칩의 접점과 기판의 접점을 금속선(Wire Bonding)이나 범프(Flip Chip)를 이용해 전기적으로 연결한다.

- 성형(Molding): 화학 수지로 칩을 감싸 외형을 완성하고 내부 회로를 보호한다.

- 최종 테스트: 패키징이 완료된 제품의 성능과 신뢰성을 검사하여 양품을 선별한다.

첨단 패키징 기술

AI 및 고성능 컴퓨팅(HPC) 시대가 도래함에 따라 미세공정의 한계를 극복하기 위한 첨단 패키징 기술이 중요해지고 있다.

- TSV(Through Silicon Via): 칩에 미세한 구멍을 뚫어 상하 칩을 수직으로 연결하는 관통 전극 기술이다. 기존 와이어 본딩보다 데이터 전송 속도가 빠르고 소비 전력이 낮다.

- HBM(High Bandwidth Memory): 여러 개의 D램을 TSV 기술로 수직 적층하여 데이터 처리 속도를 극대화한 메모리이다.

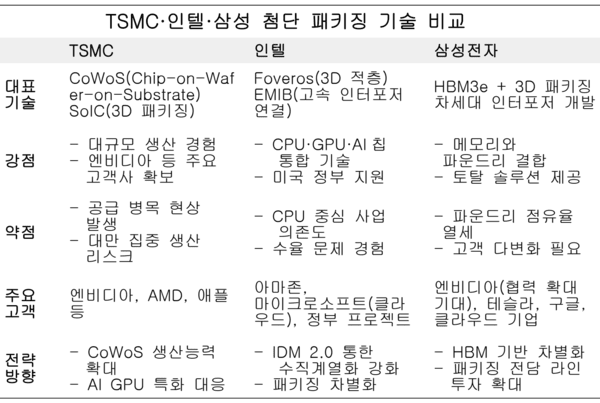

- 2.5D/3D 패키징: 서로 다른 기능을 가진 칩들을 하나의 패키지 안에 통합하는 기술이다. TSMC의 CoWoS, 인텔의 Foveros 및 EMIB, 삼성전자의 H-Cube 등이 대표적이다.

산업 구조 및 동향

과거 패키징은 인건비가 저렴한 지역의 외주 패키징 전문업체(OSAT)가 주로 수행하는 단순 공정으로 여겨졌다. 그러나 패키징 기술이 반도체 성능의 핵심 차별화 요소가 되면서 삼성전자, TSMC, 인텔과 같은 파운드리 및 종합반도체업체(IDM)들이 직접 첨단 패키징 기술 개발과 시설 투자에 나서고 있다.