칩렛

본 서비스가 제공하는 내용 및 자료가 사실임을 보증하지 않습니다. 시스템은 언제나 실수를 할 수 있습니다. 중요한 의사결정 및 법리적 해석, 금전적 의사결정에 사용하지 마십시오.

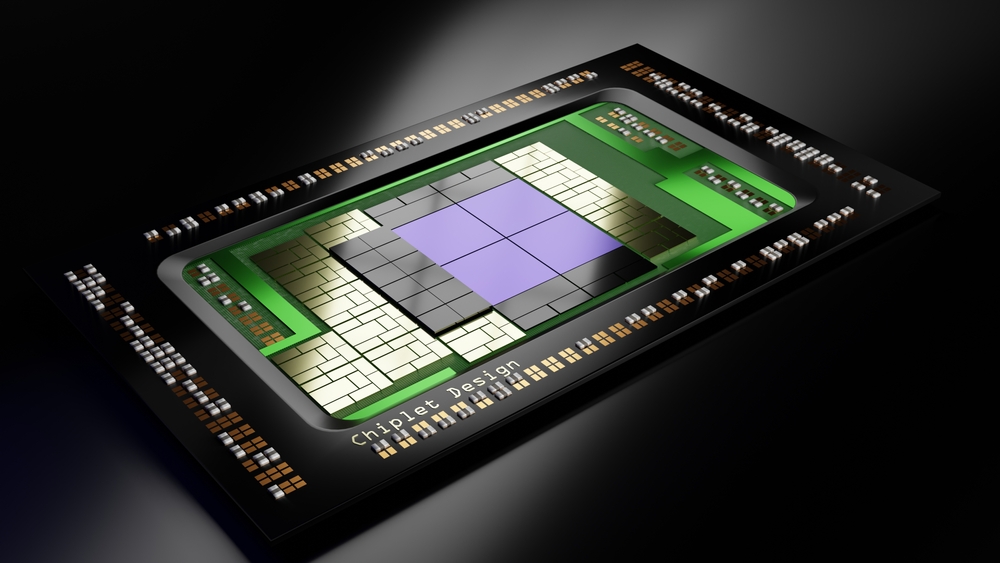

칩렛(Chiplet)은 잘 정의된 기능 하위 집합을 포함하는 작은 단위의 집적 회로(IC)이다. 단일 실리콘 조각에 모든 기능을 넣는 전통적인 단일 칩(Monolithic) 방식과 달리, 여러 개의 작은 칩을 레고 블록처럼 조합하여 하나의 패키지로 만드는 기술을 의미한다. 이를 통해 제조 수율을 높이고 비용을 절감하며, 서로 다른 공정 노드에서 생산된 칩들을 하나로 통합하는 이종 통합을 가능하게 한다.

개요

칩렛은 반도체 산업의 이종 통합 추세에 따라 등장한 기술이다. 소형화되고 전문화된 여러 개의 칩 다이(Die)를 선택하여 혼합함으로써 원하는 전체 기능을 구현한다. 이는 기존의 시스템 온 칩(SoC) 접근 방식에서 발생하는 제조상의 한계를 극복하기 위한 대안으로 주목받고 있다.

주요 장점

칩렛 기술은 비용, 성능, 설계 유연성 측면에서 다음과 같은 이점을 제공한다.

- 비용 효율성 및 수율 향상: 단일 큰 칩을 제조할 때 발생하는 높은 결함률을 줄일 수 있다. 작은 칩렛 단위로 제조하면 결함이 있는 부분만 폐기하면 되므로 전체 수율이 향상된다.

- 이종 통합(Heterogeneous Integration): 각 기능을 수행하는 칩렛을 서로 다른 공정 노드나 재료로 제작할 수 있다. 예를 들어, 최첨단 공정이 필요한 연산부는 7nm 이하 공정으로 만들고, 상대적으로 구형 공정으로도 충분한 입출력(I/O)부는 저렴한 공정으로 제작하여 결합할 수 있다.

- IP 재사용: 한 번 설계된 칩렛을 다양한 장치에서 반복적으로 사용할 수 있어 설계 시간과 비용이 절감된다.

기술적 구성 및 표준

여러 개의 칩렛이 하나의 칩처럼 동작하기 위해서는 고속 인터커넥트 기술과 고급 패키징 기술이 필수적이다.

연결 표준

서로 다른 제조사나 설계자가 만든 칩렛 간의 상호 운용성을 확보하기 위해 다음과 같은 표준 인터페이스가 사용된다.

- UCIe (Universal Chiplet Interconnect Express)

- BoW (Bunch of Wires)

- AIB (Advanced Interface Bus)

패키징 기술

칩렛은 2.5D IC 또는 3D IC와 같은 고급 패키징 기술을 통해 통합된다. 칩렛 간의 통신을 위해 인터포저(Interposer)라는 중간층이 사용되기도 하며, 이는 데이터 전송 속도를 높이고 전력 소모를 줄이는 역할을 한다.

주요 사례 및 시장 전망

주요 반도체 기업들은 이미 칩렛 기술을 자사 제품에 적극적으로 도입하고 있다.

- AMD: 젠 2(Zen 2) 아키텍처 이후의 라이젠(Ryzen) 프로세서에 칩렛 구조를 적용하여 시장 점유율을 확대하였다.

- 인텔: 메테오레이크(Meteor Lake) 등의 프로세서에서 칩렛 기반 설계를 채택하였다.

- 엔비디아: H100 가속기 등 고성능 컴퓨팅 제품군에 활용하고 있다.

시장 조사 기관에 따르면 칩렛 기술은 서버, 통신, PC, 자동차 산업 등으로 확산되어 2035년까지 약 4,110억 달러 규모의 시장을 형성할 것으로 전망된다.